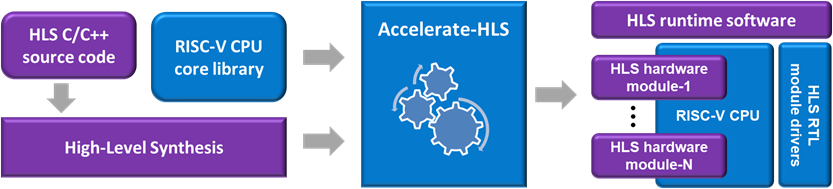

Bluespec's Accelerate-HLS tool simplifies and speeds the development of hardware using High-Level Synthesis (HLS) by offloading complex functionality that RISC-V processors can more effectively implement. For example, memory management (address translation, coherence, protection, ..) is a complex, performance-critical requirement that is outside the expertise of the average designer and problematic for HLS designs. Accelerate-HLS eliminates this problem by providing HLS designs direct access to proven, high-performance memory management that is standard fare in modern RISC-V processors.

Accelerate-HLS provides more than just RISC-V hooks into HLS. It also automatically generates the hardware-software stacks necessary to connect custom HLS designs to configurable RISC-V processors. This eliminates the time-consuming and risky manual hardware-software integration still common today.

Advantages:

|

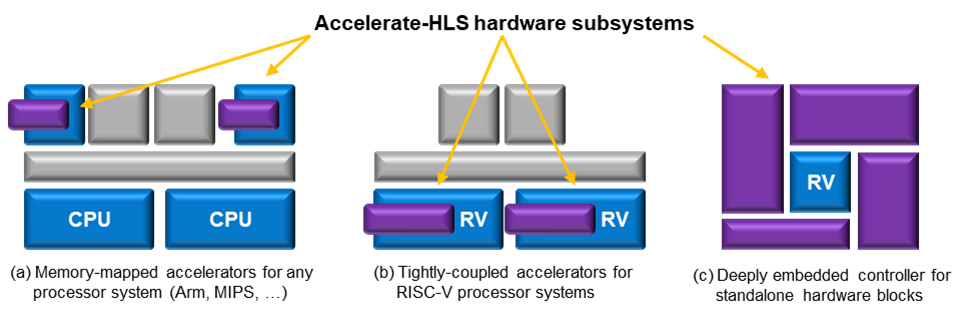

Accelerate-HLS’s key advantages derive from connecting custom hardware to RISC-V processors using tightly coupled interfaces. This enables automated correct-by-construction generation of subsystems with lower overhead, lower latency and significantly less complexity than conventional memory-mapped hardware attached to system-level interconnect. |

|

|

Automated, correct-by-construction spin design changes into working systems in minutes versus days |

Reduced system-level complexity subsystems isolate the top-level system from complexity and bugs |

|

Shared cache-coherent virtual memory eliminate tedious processor-hardware memory management |

Scales from micro-controllers to multi-core Linux full spectrum of RISC-V cores provides headroom and roadmap |

Features

|

Memory Management Physical and virtual memory Caches and tightly coupled memory Processor-HLS memory coherence Linux compatible hardware MMU |

Software execution modes Hardware-enforced atomic execution Software-managed concurrent execution Polling & Interrupts (future) Linux-managed software multi-threading |

Extended applications Hardware-acceleration Custom instructions (future) Domain-specific processors RISC-V assisted hardware |

|

Runtime configuration Program module-specific control/status registers using auto-generated firmware |

Function Callbacks (future) Hardware calls arbitrary software functions on demand |

Build automation Correct-by-construction build of complete hardware-software stack |

|

RISC-V Core Library |

|||||

|

Feature |

Microcontroller |

Bare Metal |

Linux |

Superscalar Linux |

Multi-core Linux |

|

Instruction width |

32-bit |

32 & 64 bit |

32 & 64 bit |

32 & 64 bit |

32 & 64 bit |

|

Floating point |

- |

option |

option |

Option |

option |

|

Virtual memory |

- |

- |

yes |

Yes |

yes |

|

Microarchitecture |

multi-cycle |

5-stage pipeline |

5-stage pipeline |

10-stage pipeline |

5/10-stage pipeline |

|

L1 I&D memory |

up to 256KB TCMs |

16KB - 64KB |

16KB - 64KB |

16KB - 64KB |

16KB - 64KB |

|

L2 cache memory |

- |

up to 512KB |

up to 512KB |

up to 512KB |

up to 512KB |

|

Interrupt controller |

PLIC |

PLIC |

PLIC |

PLIC |

PLIC |

|

Timer |

CLINT |

CLINT |

CLINT |

CLINT |

CLINT |

|

System bus |

AXI4, AHB |

AXI4 |

AXI4 |

AXI4 |

AXI4 |